Responsibilities

- Creating verification plans of complex digital design blocks by fully understanding the design specification and interacting with design engineers to identify important verification scenarios

- Create verification environments using SystemVerilog, SystemC or UVM

- Identify and write all types of coverage measures for stimulus and corner-cases

- Debug tests with design engineers to deliver functionally correct design blocks

- Close coverage measures to identify verification holes and to show progress towards tape-out

Essential Requirements

- Bachelor’s degree in Electrical Engineering or Computer Science

- Experience in verifying digital logic at the Register Transfer Level (RTL) using SystemVerilog or SystemC for ASICs and/or SoCs

- Experience with the creation of and usage of verification components and environments in a standard verification methodology such as UVM, OVM, or VMM

- Solid verification skills in problem solving, constrained random and directed tests, and debugging

- Be able to develop a SystemVerilog testbench from scratch

Desirable Pluses

- Master’s degree in Electrical Engineering or Computer Science

- 5+ years experience in verification of complex SoC

- Solid understanding of complete SoC design flow and verification techniques and methods

- Experience in one or more of the following application domains, is a plus

- Defining coverage space and writing coverage model

- Verification IP (VIP) development or usage

- LPDDR

- AMBA bus protocols

- Verification using SystemC

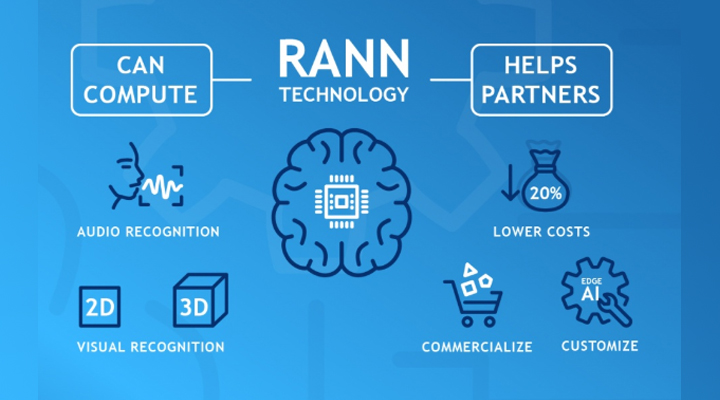

- Neural network

技能標籤: SOC, systemc, systemverilog, UVM