Who You Are

- You are an open and honest communicator who values your team

- You are innovative, enjoy bringing new ideas to the table and are receptive to ideas and feedback from others

- You’re passionate about advancing the state of the world through new technology

- You enjoy the ambiguity and pace of a startup environment

What you will be doing

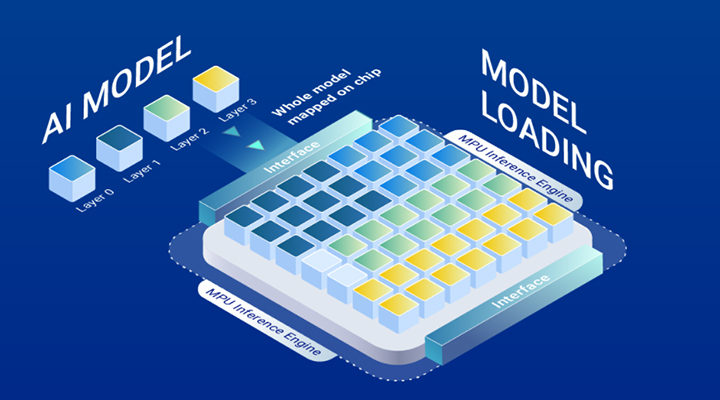

- Blocks design, SoC design and integration

- Design simulation and verification

- Run all digital design flow(synthesis/STA/lint/LEC/…)

- FPGA build up and verification

What we expect to see

- BS, MS or PhD in electrical engineering, computer engineering or computer science with a special focus on digital system design, computer architecture or computer hardware design

- 3-10 years of industry experience

- Experience in RTL design(design many modules from scratch). Verilog is required and SystemVerilog is a must

What we would be happy to see

- Experience in ARM processor, bus design, SoC integration, standard interfaces protocols and common IP blocks

- Experience in design flows for simulation, synthesis, verification, design for testing, static timing analysis, logic equivalence check, etc.

- Experience in chip tape-out and volume production, especially in sub-40nm nodes

- Skilled in system verification such as FPGA prototype buildup and debug

- Familiarity with script programming such as shell script, make, Python, etc.

- Willing to take on challenges, and effective English communications and co-work with other team members

Tagged as: arm processor, bus design, RTL, soc integration, systemverilog, verilog